# 6T and 8T SRAM Cell Simulation with Power Loss Analysis

# A. Manikandan<sup>\*</sup>

\*Assistant Professor, ECE Department, SSM Institute of Engineering and Technology, Dindigul, India

Corresponding Email: \*manikandan.aapece@ssmiet.ac.in

Received: 23 September 2021 Accepted: 10 December 2021 Published: 18 January 2022

Abstract: Reducing the power consumption in a VLSI circuits is a prime concern now a days. Memory circuits play an important role in the design of electronic small power devices. Almost every digital systems is having memory as an important part in their design. The high speed circuits dissipate a considerable amount of power in a short time. In this paper conventional SRAM cell is modified little bit to reduce the dynamic power dissipation. The overall capacitance reduced by adding few extra transistors. Because of the fact that charging and the discharging of the bit lines consumes the most power, so 6T cell and 8T cell can be used to reduce the power by adding an extra number of transistors to the pull down path. In this paper 6T SRAM cell as well as 8T SRAM cell simulated and their performance compared in terms of power dissipation.

Keywords: Power Dissipation, SRAM Cell, Power Dissipation, Tanner Tools, VLSI.

# 1. INTRODUCTION

Low power consumption and high performance are today's challenges. There is an increasing need to design portable devices that operate on low-power batteries and consume very little power. SRAM is an inherent part of most systems in the VLSI domain [1-5]. Speed and power consumption are key issues in designing SRAM circuits [6-8]. A traditional SRAM cell uses six transistors for reading and writing. It has the advantage of small footprint [9-12]. Here, reading and writing are done through a single bit line [13-15]. The logic is stable after writing, but reading requires additional circuitry such as sense amplifiers [16-20]. The conventional 8T circuit proposed in [21-24] is also simulated with conventional 6T batteries, and the transient analysis of the circuit is carried out, and the power consumption is calculated. Traditional circuits use eight transistors. The key idea of the 8T transistor to get the read output [25]. This white paper focuses on the design and simulation of a traditional

Journal of Electronics, Computer Networking and Applied Mathematics ISSN: 2799-1156 Vol: 02, No. 01, Dec 2021 -Jan 2022 http://journal.hmjournals.com/index.php/JECNAM DOI: https://doi.org/10.55529/jecnam.21.17.23

6T SRAM cell and an advanced 8T SRAM cell, and compares the power dissipation of the two cells. Simulations and analyzes done using generic 250nm model files. Result of We compared the power loss of a conventional 6T SRAM cell and an 8T SRAM cells [26-28].

### **RAM DESIGN**

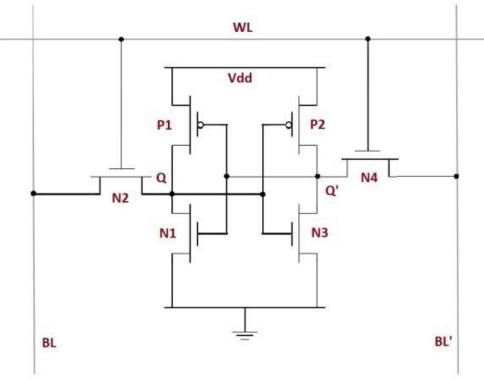

#### **Conventional 6T SRAM cell**

Figure 1 shows that a 6T SRAM cell [9] consists of PMOS and NMOS transistors. PMOS transistors are the load transistors and the lower NMOS transistors, which are connected in a cross-coupled way termed as the driver transistor. The pass transistor used to connect the cross-coupled inverter to the outside world. Word lines are used to activate or deactivate the memory writing, Data bits that have to be written are supplied via the bit lines.

Fig 1. 6T SRAM cell

Bit lines are also used to read data stored in SRAM cells. In write mode, the bit to be written is provided on the bit line with the word line asserted, and the inverted version is provided on the bit bar line. When the word line is asserted, the bit line value is latched. As a bit line, the input drives much stronger than the value previously stored in the two cross-coupled inverters, so new data is written to the cell. To read a bit, the bit line is pre charged to a logic 1, then the word line is asserted, which activates the access transistor in the design. The value stored in the SRAM is transferred to the bit lines, one of which is discharged through the drive transistor and the other is pulled up to logic 1 via the load transistors. Journal of Electronics, Computer Networking and Applied Mathematics ISSN: 2799-1156 Vol: 02, No. 01, Dec 2021 -Jan 2022 http://journal.hmjournals.com/index.php/JECNAM DOI: https://doi.org/10.55529/jecnam.21.17.23

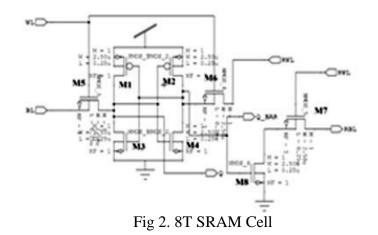

## 8T SRAM Cell

8T SRAM cells [10] use separate sections for writing and reading stored bits. M5 and M6 are access transistors used to access the inverter during write operations. Transistors M1, M3, M2, and M4 are used to store data. M1 and M3 are one inverter (inverter 1), and M2 and M4 are another inverter. (Inverter 2) Two inverters are connected back to back. The access transistor is enabled or disabled depending on the value of WL. Six transistors are used to write data into the SRAM cell, and two transistors are used to read stored data. The read array is a separate section that is active during the read operation. When data needs to be written, the access transistor is activated. The data bits are provided via the bit lines (BL). In the write operation, the data comes via the M5 transistor and passes through the second inverter and the input of inverter 1 receives the inverted value from inverter 2 and value get stored at the node Q. This way, the write operation performed. For the read operation, the data stored to RBL line when the RWL line is active.

#### Simulation

#### **6T SRAM Write operation**

For simulating the write operation of 6T SRAM cell, the cell designed using the schematic editor tool and then WL and BL lines are assigned proper signal and simulation performed for 2000ns.

## 8T SRAM write and read Operation.

For the 8T SRAM cell, the cell designed with the schematic editor and then proper bit streams are supplied in proper order to have a situation where some data are written first in the SRAM cell, then they are read via the RBL lines by activating the RWL line at the proper time. The simulation performed for 2000ns,

## 2. RESULTS AND DISCUSSION

#### **Simulation Waveforms**

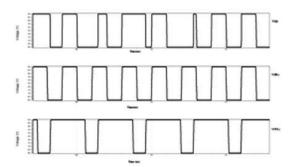

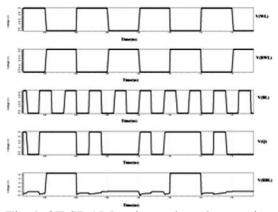

In this section, we simulate the read and write operations of 6T and 8T SRAM cells by

#### Journal of Electronics, Computer Networking and Applied Mathematics ISSN: 2799-1156 Vol: 02, No. 01, Dec 2021 -Jan 2022 http://journal.hmjournals.com/index.php/JECNAM DOI: https://doi.org/10.55529/jecnam.21.17.23

providing appropriate BL and WL signals at appropriate times. The 250 nm general library is used for this simulation. We also use the Tanner tool for design verification. In addition, we simulated the power loss of 6T and 8TSRAM cells in the case of bit "0" write and bit "1" write, and compared the power loss between 8TSRAM cells.

Fig 3. 6T SRAM write operation

In the Fig 3.shows the various signals during the SRAM write cycle. First logic 1 written to memory and after that logic 0 written. The data that is written also displayed in the waveform(Q).During the write operation the Word Line WL) lines must go to logic 1 state and either logic 0 or logic 1 can be written based on the logic provided via the Bit lines(BL).Then in Fig 4. various write cycle signals as well as the read cycle signals are shown for the 8T SRAM cell. The waveform shows how few data bits can be written into the cell and how the read operations can be performed by asserting the word line(WL) and the read word line(RWL) at proper time..All the simulations were performed for 2000ns.As seen from the waveform the read operation retrieves the stored data only when RWL is asserted.

Fig 4. 8T SRAM write and read operation

## **Power dissipation**

Table 1 shows the average power dissipated during the write 1 and write 0 cycle for 6T and 8T SRAM cell respectively. The table also shows the considerable amount of power saving when 8T SRAM simulated. This power dissipation table is for 250nm model and simulated with T-SPICE.

Copyright The Author(s) 2022. This is an Open Access Article distributed under the CC BY license. (http://creativecommons.org/licenses/by/4.0/) 20

| Operation   | Average Power<br>(6T cell) | Average Power<br>(8T cell) | Save (%) |

|-------------|----------------------------|----------------------------|----------|

| Write bit 1 | 2.3mW                      | 2.1mW                      | 8.69     |

| Write bit 0 | 1.6mW                      | 1.26mW                     | 21       |

Table 1 Average power dissipation

It has been observed from the table that '1' write cycle power dissipation reduced by 8.69% when 8T SRAM cell being used and the write 0 cycle power dissipation decreased 21 %. The above result found for 5V supply and 250nmtechnology.

| Operation   | 5V     | 1.8 V | 1.2 V   |

|-------------|--------|-------|---------|

| Write bit 1 | 2.1mW  | 79uW  | 9.2u W  |

| Write bit 0 | 1.26mW | 53uW  | 9.03u W |

Table 2 Variation of power dissipation with supply voltage for 8T SRAM

Table 2 shows the power dissipation for different supply voltages for 8T SRAM cell and found ideal for low voltge devices for which case the power dissipation Is very low.

## 3. CONCLUSIONS

As seen from this paper, the average power reduced to 21% in the case of 0-bit writing and 8.69% in the case of 1-bit writing. From this, it can be concluded that the 8T SRAM device will consume very little power as compared with the conventional 6T SRAM cell, whose results are also reported in this paper.

# 4. REFERENCES

- 1. Manikandan, A., & Jamuna, V. (2017a). Fault Tolerant Parallel Filters Based On Error Correction Codes. Journal of Advanced Research in Dynamical and Control Systems, 9(2), 1399–1404.

- 2. Manikandan, A., & Nirmal Kumar, P. (2017). Network-On-Chip by using Power Reduction Technique. International Journal of Control Theory and Applications, 10(12), 265–269.

- 3. Manikandan, A., & Nithya, P. (2017). Low-Power Content Addressable Memory Based on Sparse Clustered Networks. Journal of Chemical and Pharmaceutical Sciences, 302–304.

- 4. Manikandan, A., & Nirmal Kumar, P. (2017). Network-On-Chip by using Power Reduction Technique. International Journal of Control Theory and Applications, 10(12), 265–269.

- S. Dhanasekaran, T. Thamaraimanalan, V.Anandkumar and A. Manikandan, "Analysis And Design Of Fir Filter Using Modified Carry Look Ahead Multiplier," International Journal Of Scientific & Technology Research, Vol. 09, Issue No.03, 2020, pp. 1336-1339.

- 6. Ashokkumar, N., Nagarajan, P., Venkatramana, P. (2020). 3D(Dimensional)-Wired

Copyright The Author(s) 2022. This is an Open Access Article distributed under the CC BY license. (http://creativecommons.org/licenses/by/4.0/) 21

Vol: 02, No. 01, Dec 2021 -Jan 2022 http://journal.hmjournals.com/index.php/JECNAM DOI: https://doi.org/10.55529/jecnam.21.17.23

and Wireless Network-on-Chip (NoC). In: Ranganathan, G., Chen, J., Rocha, Á. (eds) Inventive Communication and Computational Technologies. Lecture Notes in Networks and Systems, vol 89. Springer, Singapore. https://doi.org/10.1007/978-981-15-0146-3\_12.

- N. Ashok Kumar, G. Shyni, Geno Peter, Albert Alexander Stonier, Vivekananda Ganji, "Architecture of Network-on-Chip (NoC) for Secure Data Routing Using 4-H Function of Improved TACIT Security Algorithm", Wireless Communications and Mobile Computing, vol. 2022, Article ID 4737569, 9 pages, 2022. https://doi.org/10.1155/2022/4737569

- 8. Ashokkumar N, Kavitha A. An Efficient and Novel Design of Loop filter Charge Pump and VCO for PLL using CMOS technology. International Journal of Engineering & Technology. 2018;7(3.1):39-41.

- Ashokkumar, N., Nagarajan, P., Vithyalakshmi, N., Venkataramana, P. (2019). Quad-Rail Sense-Amplifier Based NoC Router Design. In: Hemanth, J., Fernando, X., Lafata, P., Baig, Z. (eds) International Conference on Intelligent Data Communication Technologies and Internet of Things (ICICI) 2018. ICICI 2018. Lecture Notes on Data Engineering and Communications Technologies, vol 26. Springer, Cham. https://doi.org/10.1007/978-3-030-03146-6\_170.

- N. A. Kumar, P. Nagarajan, M. S. L, J. Arockia Dhanraj and T. S. Kumar, "Analysis of Millimeter-Wave based on Multichannel Wireless Networks-on-Chip," 2022 International Conference on Electronics and Renewable Systems (ICEARS), 2022, pp. 405-409, doi: 10.1109/ICEARS53579.2022.9752077.

- 11. P. Nagarajan, N. A. Kumar, J. Arockia Dhanraj, T. S. Kumar and M. Sundari L, "Delay Flip Flop based Phase Frequency Detector for Power Efficient Phase Locked Loop Architecture," 2022 International Conference on Electronics and Renewable Systems (ICEARS), 2022, pp. 410-414, doi: 10.1109/ICEARS53579.2022.9752249.

- 12. Neelima, K., Ashok Kumar Nagarajan, and Neeruganti Vikram Teja. "Digital Twin Technology Characteristics Design Implications and Challenges for Healthcare Applications." Advancement, Opportunities, and Practices in Telehealth Technology. IGI Global, 2022. 105-115.

- 13. Natarajan V, Nagarajan AK, Pandian N, Savithri VG. Low Power Design Methodology. Very-Large-Scale Integration. 2018 Feb 16:47.

- 14. Kumar, N. Ashok, S. Vishnu Priyan, P. Venkatramana, and Durgesh Nandan. "Routing Strategy: Network-on-Chip Architectures." In VLSI Architecture for Signal, Speech, and Image Processing, pp. 167-197. Apple Academic Press, 2022.

- 15. Ashokkumar, N., P. Nagarajan, and S. Ravanaraja. "Survey Exploration of Network-on-Chip Architecture." (2009).

- AshokKumar N, Nagarajan P, Selvaperumal S, Venkatramana P. Design challenges for 3 dimensional network-on-chip (NoC). InInternational Conference on Sustainable Communication Networks and Application 2019 Jul 30 (pp. 773-782). Springer, Cham.

- 17. Ashokkumar, N., and A. Kavitha. "Transition level energy consumption of NoC (network-on-chip) using data encoding techniques." 2015 2nd International Conference on Computing for Sustainable Global Development (INDIACom). IEEE, 2015.

- 18. Kavitha, T. & Reddy, K. & Sravani, J. (2021). Performance Investigation of Fiber to

Journal of Electronics, Computer Networking and Applied Mathematics ISSN: 2799-1156 Vol: 02, No. 01, Dec 2021 - Jan 2022

http://journal.hmjournals.com/index.php/JECNAM DOI: https://doi.org/10.55529/jecnam.21.17.23

the Home (FTTH) Ingress Network Based on GPON with Optisystem. 10.1007/978-981-15-5029-4\_9.

- 19. Arulmary, A., Rajamani, V., & Kavitha, T. (2020). Study of uniformly doped nano scale single-walled CNTFET under dark and illuminated conditions. Microelectron. J., 104, 104889.

- 20. Kavitha, T., & Pavani, R. (2019). Dense wavelength division multiplexing using dispersion fibre with erbium doped fiber amplifier. International Journal of Innovative Technology and Exploring Engineering, 8.

- 21. Kayalvizhi, B., Anies Fathima, N., & Kavitha, T. (2015). Booth recoded Wallace Tree multiplier using and based digitally controlled delay lines. ARPN Journal of Engineering and Applied Sciences, 10, pp.2707–2713.

- 22. Kiruthika, R., Kavitha, T., & Aravintha, R. (2015). Clock gating optimization technique using buffer gates. International Journal of Applied Engineering Research. 10(20), pp.17940–17944.

- 23. Abrose, N., & Banu, T.Kavitha. (2015). A two dimensional threshold voltage analytical modelling and simulation of multigate MOSFETs for low power VLSI applications. International Journal of Applied Engineering Research. 10(20), pp.17355–17359.

- 24. Nagarajan, P., Kavitha, T., & Venkatraman, P. (2020). Design and evaluation of power efficient shift register featuring low power automatic manufacturing systems. Solid State Technology. 63(5).

- S. Dhanasekaran, T. Thamaraimanalan, R. SudhaAnandhi and A. Mohanapriya, "Comparative Analysis of Low Power and High Speed Performance in 8-bit Different Multipliers," Journal of Advanced Research in Dynamical & Control Systems, Vol. 10, 04-Special Issue, 2018, pp. 89-93.

- 26. S. Dhanasekaran, N.Ragavi, Yamini.E. (2014). Implementation of low power Low noise probabilistic-based logic designs. International Journal of Computer Science and Mobile Computing. vol.3(10). pp. 840-844.

- 27. Ushus George, S. Dhanasekaran. (2014). A Novel Design Approach to Achieve Fault Coverage in Sequential Circuits. International Journal of Engineering Science and Innovative Technology.vol 3(1).