Design And Verification of Advanced Peripheral Bus Protocol Using Uvm

Keywords:

APB, AMBA, UVM, HDL, UARTAbstract

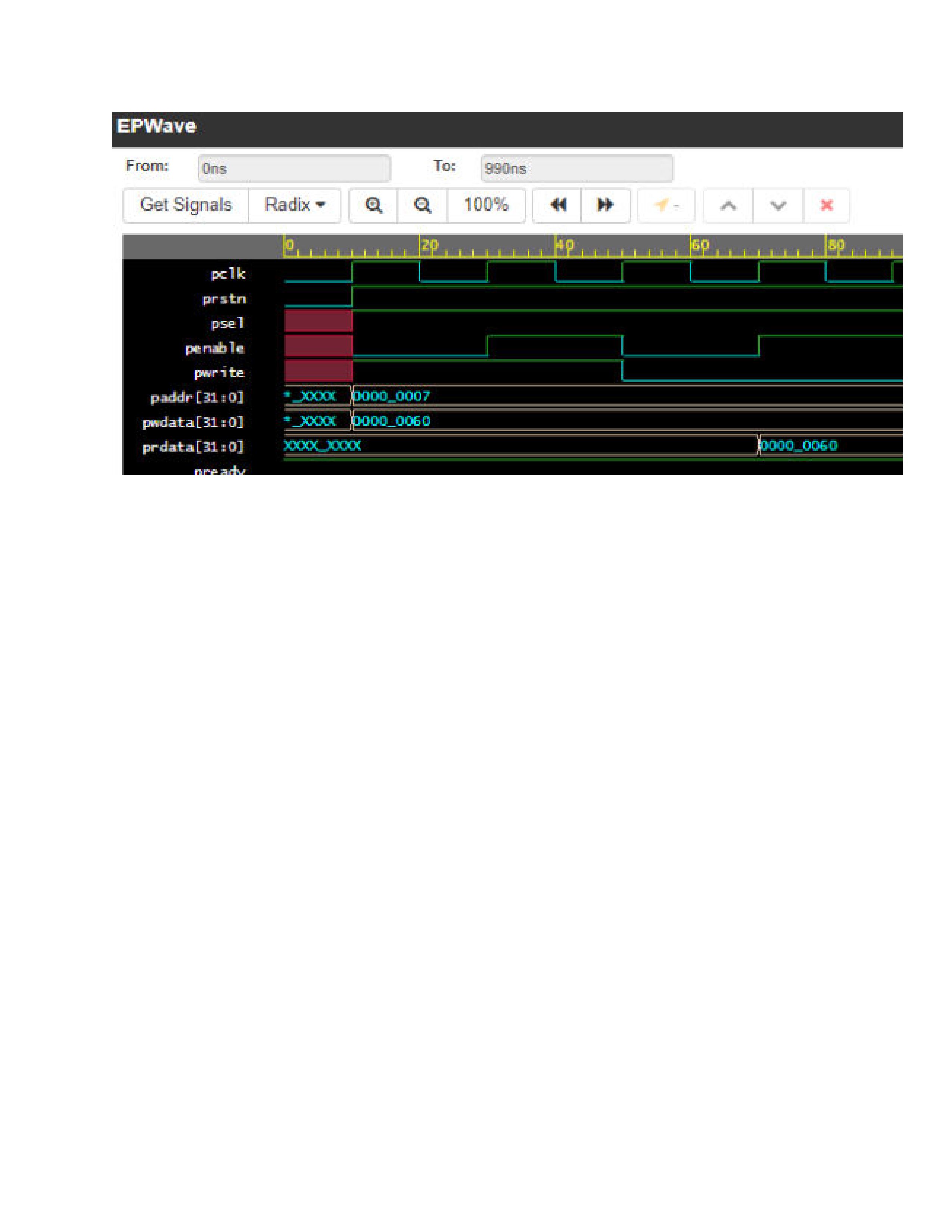

The System on chip uses advanced micro controller bus architecture is on chip bus introduced by ARM. Advanced peripheral bus is the component of the AMBA bus architecture. APB is low bandwidth, low power and low performance it used to connect the peripherals like UART, Keypad, Timer and other peripheral devices to the bus architecture. This introduces the AMBA APB bus using UVM architecture design. The design created using the Verilog and HDL and tested by Verilog test bench and design is verified using universal verification methodology. In this, we have a master and a slave. The master sends the control signals as a packet to the slave and the slave addresses the packet if both are equal we are getting transaction of write and read data, Where the master send the address slave recognize and it sends the signal to the master as a read data.

Published

How to Cite

Issue

Section

Copyright (c) 2021 Authors

This work is licensed under a Creative Commons Attribution 4.0 International License.