Modified Efficient OMS LUT Design for Memory-Based Multiplication

Keywords:

Digital Signal Processing, VLSI, FIR Filter, Memory-Based Computations, LUT.Abstract

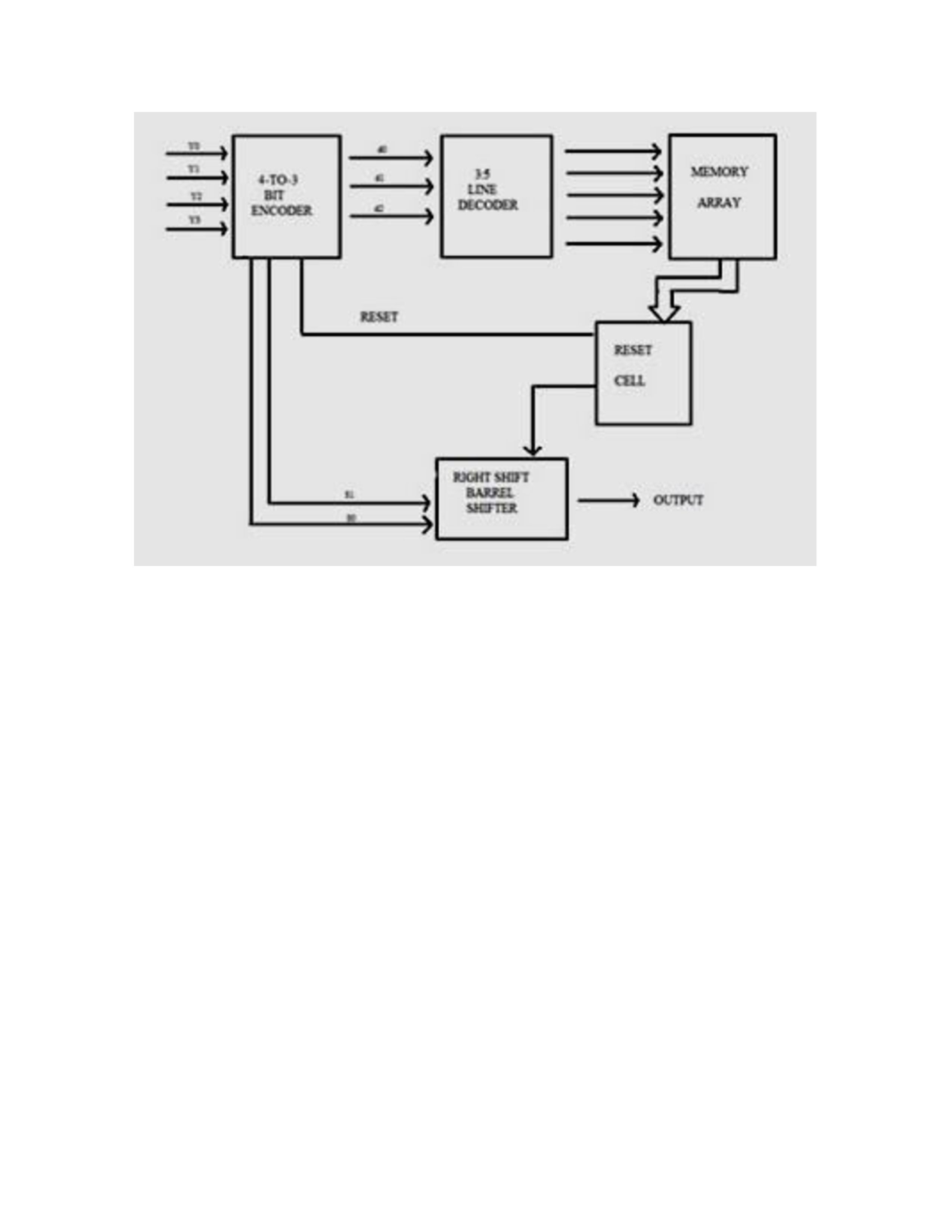

This paper proposes an efficient LUT (Look-Up-Table) design called Efficient EOMS (Efficient-OMS Design) for memory-based operations. This proposed design can be used for FPGA implementation as well as ASIC. The proposed design is a better choice than ordinary OMS (Odd Multiplier Store) and is preferred in many DSP calculations where one of the inputs to the filter coefficients is fixed. In this design (N+1), the possible product terms of the input multiplicands with fixed coefficients are stored directly in memory. Doing so allows for a simpler and faster design, unlike the previous proposal OMS (Odd Multiple Storage).Designs that extract odd multiples of the product term can significantly reduce path delay and area complexity with very simple control circuitry. Using (N+1) technology can significantly reduce the area compared to ordinary OMS technology. Additionally, the EOMS technical design is coded in Verilog and simulated and synthesized using Xilinx tools.

Published

How to Cite

Issue

Section

Copyright (c) 2022 Authors

This work is licensed under a Creative Commons Attribution 4.0 International License.